# DATA SHEET

| Part No.         | AN12978A       |

|------------------|----------------|

| Package Code No. | UBGA015-W-2020 |

### Contents

| Overview                                                   | 3  |

|------------------------------------------------------------|----|

| ■ Features                                                 | 3  |

| Applications                                               | 3  |

| Package                                                    | 3  |

| ■ Туре                                                     | 3  |

| Application Circuit Example (Block Diagram)                | 4  |

| Pin Descriptions                                           | 5  |

| Absolute Maximum Ratings                                   | 6  |

| ■ Operating Supply Voltage Range                           | 6  |

| Electrical Characteristics                                 | 7  |

| ■ Electrical Characteristics (Reference values for design) | 9  |

| ■ Technical Data                                           | 10 |

| Usage Notes                                                | 20 |

|                                                            |    |

#### AN12978A

# AN12978A Monaural BTL amplifier IC with built-in AGC (I<sup>2</sup>C bus-control correspondence)

#### Overview

AN12978A is the monaural BTL amplifier which contained the AGC circuit for clip prevention of a speaker output. This IC performs a mode change by the I<sup>2</sup>C bus control system. (Standby function ON/OFF change etc.)

#### Features

- Selection by I<sup>2</sup>C bus control is possible in the on-level of AGC. (3-bit, 8-step)

- Selection by I<sup>2</sup>C bus control is possible in an attack/recovery time of AGC. (attack: 2-bit, recovery: 3-bit)

- •The resistance and the capacitor of a detector circuit which were being used for the conventional AGC are unnecessary.

- In order to realize high efficiency of output power, it adopts CMOS power amplifier circuit.

- Built-in shutdown function.

- Built-in Gv-Switch.

#### Applications

• Audio amplifier for mobile, such as a cellular phone

#### Package

- 15 pin Wafer level chip size package (WLCSP) Size: 2.0 mm × 2.0 mm (0.5 mm pitch)

- Type

- Bi-CMOS IC

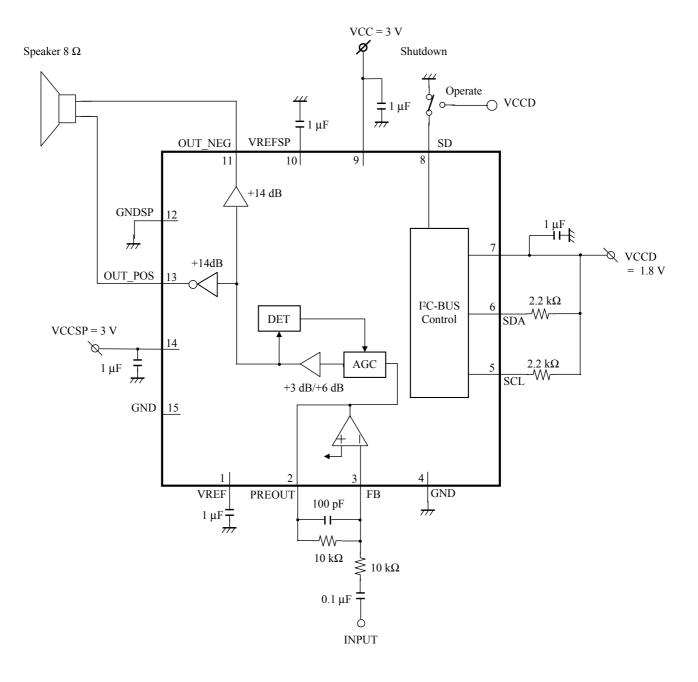

#### ■ Application Circuit Example (Block Diagram)

Note) 1. This circuit and these circuit constants show an example and do not guarantee the design as a mass-production set. 2. The threshold voltage at 8pin has the VCCD dependency.

# Panasonic

#### Pin Descriptions

| Pin No. | Pin name | Туре           | Description                                    |  |  |  |

|---------|----------|----------------|------------------------------------------------|--|--|--|

| 1       | VREF     | Output         | Reference Voltage Output                       |  |  |  |

| 2       | PREOUT   | Output         | Pre-amplifier Output                           |  |  |  |

| 3       | FB       | Input          | Pre-amplifier Negative Feedback Input          |  |  |  |

| 4       | GND      | Ground         | Ground                                         |  |  |  |

| 5       | SCL      | Input          | SCL Input on I <sup>2</sup> C-bus Control      |  |  |  |

| 6       | SDA      | Input / Output | SDA Input on I <sup>2</sup> C-bus Control      |  |  |  |

| 7       | VCCD     | Power Supply   | Power supply for logic circuit                 |  |  |  |

| 8       | SD       | Input          | Shutdown Control                               |  |  |  |

| 9       | VCC      | Power Supply   | Power supply                                   |  |  |  |

| 10      | VREFSP   | Output         | Reference Voltage Output for Speaker Amplifier |  |  |  |

| 11      | OUT_NEG  | Output         | Speaker Output (Negative Phase)                |  |  |  |

| 12      | GNDSP    | Ground         | Ground for Speaker Amplifier                   |  |  |  |

| 13      | OUT_POS  | Output         | Speaker Output (Positive Phase)                |  |  |  |

| 14      | VCCSP    | Power Supply   | Power supply for Speaker Amplifier             |  |  |  |

| 15      | GND      | Ground         | Ground                                         |  |  |  |

#### Absolute Maximum Ratings

| A No. | Parameter                     | Symbol Rating    |             | Unit | Note |

|-------|-------------------------------|------------------|-------------|------|------|

|       | 1 Supply voltage              |                  | 5.5         |      |      |

| 1     |                               |                  | 3.6         | V    | *1   |

|       |                               |                  | 5.5         |      |      |

| 2     | Supply current                | I <sub>CC</sub>  |             | А    |      |

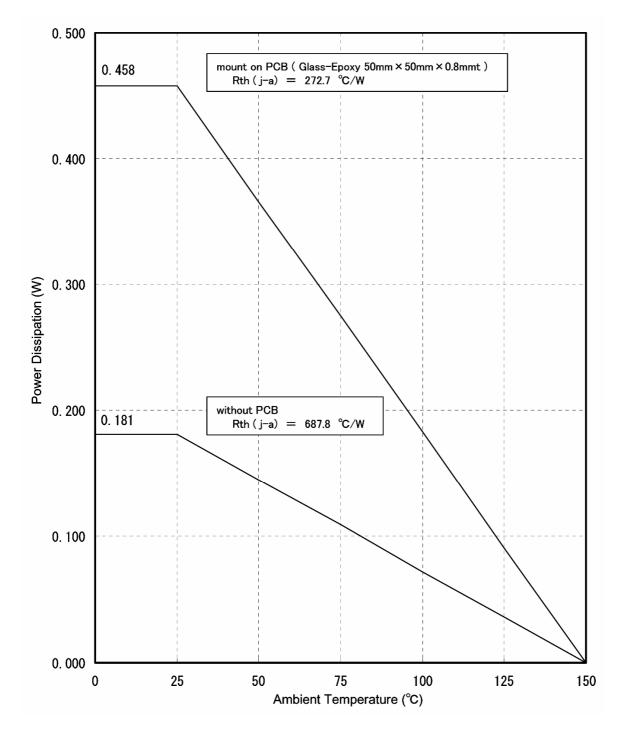

| 3     | Power dissipation             | P <sub>D</sub>   | 120         | mW   | *2   |

| 4     | Operating ambient temperature | T <sub>opr</sub> | -20 to +70  | °C   | *3   |

| 5     | Storage temperature           | T <sub>stg</sub> | -55 to +150 | °C   | *3   |

Note) \*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2: The power dissipation shown is the value at  $T_a = 70^{\circ}$ C for the independent (unmounted) IC package without a heat sink.

When using this IC, refer to the  $\bullet$  P<sub>D</sub> – T<sub>a</sub> diagram in the Technical Data and use under the condition not exceeding the allowable value.

\*3: Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

#### Operating Supply Voltage Range

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol | Range      | Unit | Note |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VCC    | 2.7 to 4.5 |      |      |

| Several to and the several s | VCCD   | 1.7 to 2.6 | N V  | *1   |

| Supply voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VCCD   | 1.7 to 3.3 |      | *2   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VCCSP  | 2.7 to 4.5 |      |      |

Note) 1. The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

2. \*1: The values under Fast mode.

\*2: The values under Standard mode.

#### AN12978A

#### Electrical Characteristics at VCC = 3.0 V , VCCD = 1.8 V , VCCSP = 3.0 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

| в    | Parameter                                         | Symbol | Quanditiana                                                                                                |      | Limits |      | 1.1 :4 | No |

|------|---------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------|------|--------|------|--------|----|

| No.  | 0.                                                |        | Conditions                                                                                                 | Min  | Тур    | Max  | Unit   | te |

| Circ | uit Current                                       | -      |                                                                                                            |      |        |      |        |    |

| 1    | Circuit current at non-signal 1<br>(VCC)          | IVCC1A | VCC = 3.0V, Non-signal<br>STB = OFF, SP = ON, AGC = ON                                                     | 0.5  | 2.4    | 4.5  | mA     |    |

| 2    | Circuit current at non-signal 2<br>(VCCSP)        | IVCC2A | VCCSP = 3.0V, Non-signal<br>STB = OFF, SP = ON, AGC = ON                                                   | 1.0  | 6.5    | 15.5 | mA     |    |

| 3    | Circuit current at non-signal 3<br>(VCCD)         | IVCC3A | VCCD = 1.8V, Non-signal<br>STB = OFF, SP = ON, AGC = ON                                                    |      | 0.1    | 10   | μΑ     |    |

| 4    | Circuit current at standby mode 1<br>(VCC)        | IVCC1B | VCC = 3.0V, Non-signal<br>STB = ON, SP = OFF, AGC = ON                                                     |      | 0.1    | 1.0  | μΑ     |    |

| 5    | Circuit current at standby mode 2<br>(VCCSP)      | IVCC2B | VCCSP = 3.0V, Non-signal<br>STB = ON, SP = OFF, AGC = ON                                                   |      | 0.1    | 1.0  | μΑ     |    |

| 6    | Circuit current at standby mode 3<br>(VCCD)       | IVCC3B | VCCD = 1.8V, Non-signal<br>STB = ON, SP = OFF, AGC = ON                                                    |      | 0.1    | 1.0  | μΑ     |    |

| 7    | Circuit current at speaker save mode 1<br>(VCC)   | IVCC1C | VCC = 3.0 V, Non-signal<br>STB = OFF, SP = OFF, AGC = ON                                                   | 0.5  | 2.4    | 4.5  | mA     |    |

| 8    | Circuit current at speaker save mode 2<br>(VCCSP) |        |                                                                                                            |      | 0.3    | 1.0  | mA     |    |

| 9    | Circuit current at speaker save mode 3<br>(VCCD)  | IVCC3C | VCCD = 1.8 V, Non-signal<br>STB = OFF, SP = OFF, AGC = ON                                                  |      | 0.1    | 10   | μΑ     |    |

| Inpu | t/output characteristics                          |        |                                                                                                            |      |        |      |        | _  |

| 11   | SP reference output level                         | VSPO   | Vin = -31.0  dBV, f = 1  kHz<br>RL = 8 $\Omega$ , GAIN = +23 dB                                            | -9.5 | -8.0   | -6.5 | dBV    |    |

| 12   | SP reference output distortion                    | THSPO  | Vin = $-31.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+23 \text{dB}$ to<br>THD5th             |      | 0.07   | 0.5  | %      |    |

| 13   | SP output noise voltage                           | VNSPO  | Non-Signal<br>using A curve filter<br>GAIN = +23 Db                                                        |      | -78    | -71  | dBV    |    |

| 14   | SP maximum rating output                          | VMSPO  | THD = 10%, f = 1 kHz<br>RL = 8 $\Omega$ , AGC = OFF                                                        | 300  | 500    |      | mW     |    |

| 15   | SP output level at power save                     | VSSPO  | Vin = $-31.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+23 \text{ dB}$<br>using A curve filter |      | -114   | -90  | dBV    |    |

| 16   | SP AGC output level 1                             | VSPOA1 | Vin = $-17.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+23 \text{ dB}$<br>AGC-Level = 4 dBV    | 3.0  | 4.0    | 5.0  | dBV    |    |

| 17   | SP AGC output level 2                             | VSPOA2 | Vin = $-12.0 \text{ dBV}$ , f = 1 kHz<br>RL = 8 $\Omega$ , GAIN = $+23 \text{ dB}$<br>AGC-Level = 4 dBV    | 3.0  | 4.0    | 5.0  | dBV    |    |

# Electrical Characteristics at VCC = 3.0 V, VCCD = 1.8 V, VCCSP = 3.0 V (continued) Note) $T_a = 25^{\circ}C \pm 2^{\circ}C$ unless otherwise specified.

| в     | Deveneter                             | Current el                  | Conditions                           |               | Limits |                   | 1 1  | No |

|-------|---------------------------------------|-----------------------------|--------------------------------------|---------------|--------|-------------------|------|----|

| No.   | Parameter                             | Symbol                      | Conditions                           | Min           | Тур    | Max               | Unit | te |

| l²C i | nterface                              |                             |                                      |               |        |                   |      |    |

| 43    | SCL, SDA signal input Low Level       | V <sub>IL</sub>             |                                      | - 0.5         |        | $0.3 \times VCCD$ | V    |    |

| 44    | SCL, SDA signal input Low Level       | V <sub>IH</sub>             |                                      | 0.7 ×<br>VCCD |        | VCCD<br>+ 0.5     | V    |    |

| 45    | SDA output signal Low Level           | V <sub>OL</sub>             | Open corrector<br>Sync current: 3 mA | 0             |        | $0.2 \times VCCD$ | V    |    |

| 46    | SCL,SDA Signal Input Current          | Ii                          | Input voltage: 0.1 V to 1.7 V        | -10           | _      | 10                | μΑ   |    |

| 47    | SCL maximum frequency of signal input | $\mathbf{f}_{\mathrm{SCL}}$ |                                      | 0             |        | 400               | kHz  |    |

| The   | threshold voltage at 8-pin            |                             |                                      |               |        |                   |      |    |

| 48    | SD input Low Level                    | Vresetlth                   |                                      |               |        | 0.1 ×<br>VCCD     | V    |    |

| 49    | SD input High Level                   | Vresethth                   |                                      | 0.9 ×<br>VCCD |        |                   | V    |    |

#### AN12978A

## Panasonic

#### ■ Electrical Characteristics (Reference values for design) at VCC = 3.0 V , VCCD = 1.8 V , VCCSP = 3.0 V

Note)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| В                   | B Parameter                                                         |                              | Conditions        |     | Limits |     | Unit | No |

|---------------------|---------------------------------------------------------------------|------------------------------|-------------------|-----|--------|-----|------|----|

| No.                 | Parameter                                                           | Symbol                       | Symbol Conditions |     | Тур    | Max | Unit | te |

| I <sup>2</sup> C in | terface                                                             |                              |                   |     |        |     |      |    |

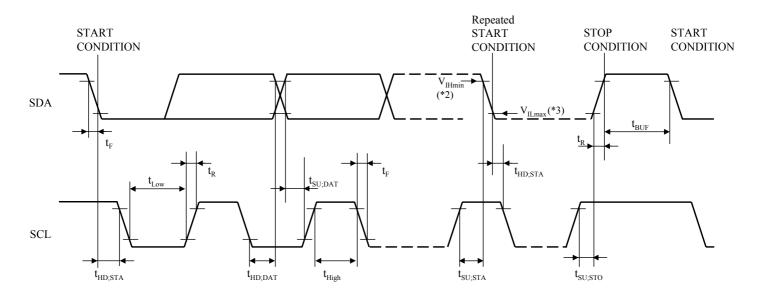

| 66                  | Bass free time between a condition of stop and a condition of start | t <sub>BUF</sub>             |                   | 1.3 |        |     | μs   | *1 |

| 67                  | Setup time of a condition of start                                  | t <sub>SU;STA</sub>          |                   | 0.6 |        |     | μs   | *1 |

| 68                  | Hold time of a condition for start                                  | t <sub>HD;STA</sub>          |                   | 0.6 |        |     | μs   | *1 |

| 69                  | "L" time of SCL clock                                               | $t_{\text{Low}}$             |                   | 1.3 |        |     | μs   | *1 |

| 70                  | "H" time of SCL clock                                               | $\mathbf{t}_{\mathrm{High}}$ |                   | 0.6 |        |     | μs   | *1 |

| 71                  | Rising time of SDA, SCL signal                                      | t <sub>R</sub>               |                   |     |        | 0.3 | μs   | *1 |

| 72                  | Fall time of SDA,SCL signal                                         | t <sub>F</sub>               |                   |     |        | 0.3 | μs   | *1 |

| 73                  | Data setup time                                                     | t <sub>su;dat</sub>          |                   | 0.1 |        |     | μs   | *1 |

| 74                  | Data hold time                                                      | t <sub>HD;DAT</sub>          |                   | 0   |        | 0.9 | μs   | *1 |

| 75                  | Rising up time of a condition of stop                               | t <sub>SU;STO</sub>          |                   | 0.6 |        |     | μs   | *1 |

Note) \*1: All values are  $V_{IHmin} \left(*2\right)$  and  $V_{ILmax} \left(*3\right)$  level standard.

\*2:  $V_{IHmin}$  is the minimum limit of the signal input high level.

\*3:  $V_{{\rm IL}{\rm max}}$  is the maximum limit of the signal input low level.

#### Technical Data

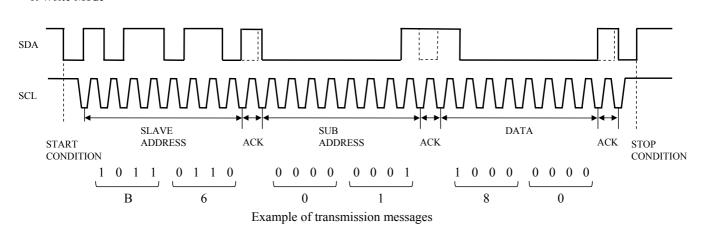

Two transmission messages (i.e., the SCL and SDA) are sent in synchronous serial transmission. The SCL is a clock with fixed frequency. The SDA indicates address data for the control of the reception side, and is sent in parallel in synchronization with the SCL. The data is transmitted in 8-bit, 3 octets (bytes) in principle, where every octet has an acknowledge bit. The following description provides information on the structure of the frame.

#### <Start Conditions>

When the level of the SDA changes to low from high while the level of the SCL is high, the data reception of the receiver will be enabled.

#### <Stop Conditions>

When the level of the SDA changes to high from low while the level of the SCL is high, the data reception of the receiver will be aborted.

#### <Slave Address>

The slave address is a specified one unique to each device. When the address of another device is sent, the reception will be aborted.

#### <Sub Address>

The sub address is a specified one unique to each function.

#### <Data>

Data is information under control.

#### <Acknowledge Bit>

The acknowledge bit is used to enable the master to acknowledge the reception of data for each octet. The master acknowledges the data reception of the receiver by transmitting a high-level signal to the receiver and receiving a low-level signal returned from the receiver as shown by the dotted lines in Fig. The communication will be aborted if the low signal is not returned.

The SDA will not change when the level of the SCL is high except start or stop conditions are enabled.

- I<sup>2</sup>C-bus Mode (continued)

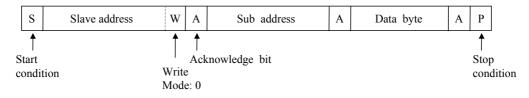

- 1. Write Mode (continued)

- (a) I<sup>2</sup>C-bus PROTOCOL

- Slave address: 10110110 (B6Hex)

- Format (normal)

#### (b) Auto increment

- · Sub-address 0\*Hex: Auto increment mode

- (When the data is sent in sequence, the sub address will change one by one and the data will be input.)

• Auto increment mode

| 110 |               |    |             |   |        |   |        |   | )     | )      |   |   |

|-----|---------------|----|-------------|---|--------|---|--------|---|-------|--------|---|---|

| S   | Slave address | WA | Sub address | A | Data 1 | Α | Data 2 | A | R     | Data n | A | Р |

| -   |               |    |             |   |        |   |        |   | $\pi$ |        |   |   |

#### (c) Initial condition

The initial state of the device is not guaranteed. Therefore, the input of 00Hex resister-D0 (Note.1) will be absolutely 0, when the power is turned ON.

(d) Sub-address Byte and Data Byte Format

| Out address | MSB                                              |                                                                            | Data byte           |                      |                                                                             |                                                      |                                                      |                      |  |  |

|-------------|--------------------------------------------------|----------------------------------------------------------------------------|---------------------|----------------------|-----------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------|--|--|

| Sub-address | D7                                               | D6                                                                         | D5                  | D4                   | D3                                                                          | D2                                                   | D1                                                   | D0                   |  |  |

| *0Hex       | $GAIN 0 \rightarrow +23 dB 1 \rightarrow +26 dB$ | AGC-ON<br>VCCSP<br>dependence<br>$0 \rightarrow OFF$<br>$1 \rightarrow ON$ | 0<br>(Note.2)       | 0<br>(Note.2)        | $\begin{array}{l} AGC \\ 0 \rightarrow OFF \\ 1 \rightarrow ON \end{array}$ | SP Save<br>$0 \rightarrow ON$<br>$1 \rightarrow OFF$ | Standby<br>$0 \rightarrow ON$<br>$1 \rightarrow OFF$ | 0<br>(Note.1)        |  |  |

| *1Hex       | AGC-ON<br>data bit3                              | AGC-ON<br>data bit2                                                        | AGC-ON<br>data bit1 | AGC-REC<br>data bit3 | AGC-REC<br>data bit2                                                        | AGC-REC<br>data bit1                                 | AGC-ATT<br>data bit2                                 | AGC-ATT<br>data bit1 |  |  |

| *2Hex       | 0<br>(Note.2)                                    | 0<br>(Note.2)                                                              | 0<br>(Note.2)       | *                    | *                                                                           | 0<br>(Note.2)                                        | 0<br>(Note.2)                                        | 0<br>(Note.2)        |  |  |

<00Hex Register> D0, D4, D5: Always set to 0 D1: Standby ON/OFF switch

- D2: SP Save ON/OFF switch

- D3: AGC ON/OFF switch

- D6: AGC-ON VCCSP dependence ON/OFF selection

D7: GAIN +17 dB/+20 dB selection

- <01Hex Register>

- D0, D1 : AGC-attack-time selection

- D2, D3, D4: AGC-recovery-time selection

- D5,D6,D7: AGC-on-level selection

<02Hex Register>

D0 to D7: Always set to 0 (test & adjust mode)

Please use these bit only Data = "0", because they are used by our company's final test and fine-tuning AGC-on level.

• I<sup>2</sup>C-bus Mode (continued)

- 1. Write Mode (continued)

- (e) AGC-attack-time selection

|    | ′rite<br>Register | Attack |

|----|-------------------|--------|

| D1 | D0                | time   |

| 0  | 0                 | 0.5 ms |

| 0  | 1                 | 1 ms   |

| 1  | 0                 | 2 ms   |

| 1  | 1                 | 4 ms   |

#### (f) AGC-recovery-time selection

| 0  | Write<br>01Hex Register |    |        |  |  |  |  |  |

|----|-------------------------|----|--------|--|--|--|--|--|

| D4 | D3                      | D2 | time   |  |  |  |  |  |

| 0  | 0                       | 0  | 1.0 s  |  |  |  |  |  |

| 0  | 0                       | 1  | 1.5 s  |  |  |  |  |  |

| 0  | 1                       | 0  | 2.0 s  |  |  |  |  |  |

| 0  | 1                       | 1  | 3.0 s  |  |  |  |  |  |

| 1  | 0                       | 0  | 4.0 s  |  |  |  |  |  |

| 1  | 0                       | 1  | 6.0 s  |  |  |  |  |  |

| 1  | 1                       | 0  | 8.0 s  |  |  |  |  |  |

| 1  | 1                       | 1  | 12.0 s |  |  |  |  |  |

(g) AGC-on-level selection (at VCC = 3.0 V, VCCSP = 3.0 V)

| Write<br>01Hex Register |    | AGC<br>On | Output<br>Po ( RL = 8W ) | VCCSP<br>(推奨値) |         |  |

|-------------------------|----|-----------|--------------------------|----------------|---------|--|

| D7                      | D6 | D5        | Level                    | 10(IL-0W)      | (延关恒)   |  |

| 0                       | 0  | 0         | 1 dBV                    | 157 mW         |         |  |

| 0                       | 0  | 1         | 2 dBV                    | 198 mW         |         |  |

| 0                       | 1  | 0         | 3 dBV                    | 249 mW         |         |  |

| 0                       | 1  | 1         | 4 dBV                    | 314 mW         | 3.0 V ≤ |  |

| 1                       | 0  | 0         | 5 dBV                    | 395 mW         | 3.3 V ≤ |  |

| 1                       | 0  | 1         | 6 dBV                    | 498 mW         | 3.7 V ≤ |  |

| 1                       | 1  | 0         | 7 dBV                    | 626 mW         | 4.1 V ≤ |  |

| 1                       | 1  | 1         | 8 dBV                    | 789 mW         | 4.5 V   |  |

(h) AGC-on-level VCCSP dependence mode (at AGC On Level = 4 dBV)

AGC ON level increases by 0.75 dBV with each 0.3 V increase of VCCSP, and baseline of VCCSP is 3.0 V at AGC-onlevel VCCSP dependence mode. When VCCSP is 3.0 V, AGC ON level is set according to table (g).

| VCCSP | AGC On<br>Level | Output<br>Po<br>( RL = 8 Ω) | VCCSP | AGC On<br>Level | Output<br>Po<br>( RL = 8 Ω) |

|-------|-----------------|-----------------------------|-------|-----------------|-----------------------------|

| 2.7 V | 3.25 dBV        | 264 mW                      | 3.9 V | 6.25 dBV        | 527 mW                      |

| 3.0 V | 4 dBV           | 314 mW                      | 4.2 V | 7 dBV           | 626 mW                      |

| 3.3 V | 4.75 dBV        | 373 mW                      | 4.5 V | 7.75 dBV        | 745 mW                      |

| 3.6 V | 5.5 dBV         | 444 mW                      |       |                 |                             |

- I<sup>2</sup>C-bus Mode (continued)

- 2. Read Mode

- (a) I<sup>2</sup>C-bus PROTOCOL

- Slave address 10110111(B7Hex)

- Format

| S    | Slave address | R | Α | Data 0 | A | Data 1 | A | Data 2 | A | Р |

|------|---------------|---|---|--------|---|--------|---|--------|---|---|

| Read |               |   |   |        |   |        |   |        |   |   |

Mode: 1

Note) At the slave address input, it is sequentially output from data 0. There is no necessity for inputting the sub-address.

#### (b) Sub-address Byte and Data Byte Format

|        | MSB Data byte |             |             |             |             |             |             |             |

|--------|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|        | D7            | D6          | D5          | D4          | D3          | D2          | D1          | D0          |

| Data 0 | Sub address   | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address |

|        | *0Hex         | *0Hex       | *0Hex       | *0Hex       | *0Hex       | *0Hex       | *0Hex       | *0Hex       |

|        | Latch data    | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  |

|        | [D7]          | [D6]        | [D5]        | [D4]        | [D3]        | [D2]        | [D1]        | [D0]        |

| Data 1 | Sub address   | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address |

|        | *1Hex         | *1Hex       | *1Hex       | *1Hex       | *1Hex       | *1Hex       | *1Hex       | *1Hex       |

|        | Latch data    | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  |

|        | [D7]          | [D6]        | [D5]        | [D4]        | [D3]        | [D2]        | [D1]        | [D0]        |

| Data 2 | Sub address   | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address | Sub address |

|        | *2Hex         | *2Hex       | *2Hex       | *2Hex       | *2Hex       | *2Hex       | *2Hex       | *2Hex       |

|        | Latch data    | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  | Latch data  |

|        | [D7]          | [D6]        | [D5]        | [D4]        | [D3]        | [D2]        | [D1]        | [D0]        |

#### • Operating temperature guarantee of I<sup>2</sup>C-bus Control

The performance in the ambient temperature of operation is guaranteed theoretically in the design at normal temperature  $(25^{\circ}C)$  by inspecting it at a speed of the clock that is about 50% earlier regarding the operating temperature guarantee of I<sup>2</sup>C-bus Control.

But the following characteristics are logical values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, Panasonic will respond in good faith to customer concerns.

- Usage note of I<sup>2</sup>C bus

- The I<sup>2</sup>C bus of this product is designed to correspond to Standard mode (100 Kbps) and Fast mode (400 Kbps) in Philips Corporation I<sup>2</sup>C specification version 2.1. However, not correspond to High Speed mode (to 3.4 Mbps).

- This product operate as a slave device in I<sup>2</sup>C bus system.

- This product is not confirm to operate in multi-master bus system and mixing -speed bus system. And this product is not confirm connectivity to CBUS receiver. If using this product in these mode, please confirm availability to our company.

- Purchase of Panasonic I<sup>2</sup>C components conveys a license to use these components in an I<sup>2</sup>C systems under the Philips I<sup>2</sup>C patent right on condition that using condition conform to I<sup>2</sup>C standard specification approved by Philips Corporation.

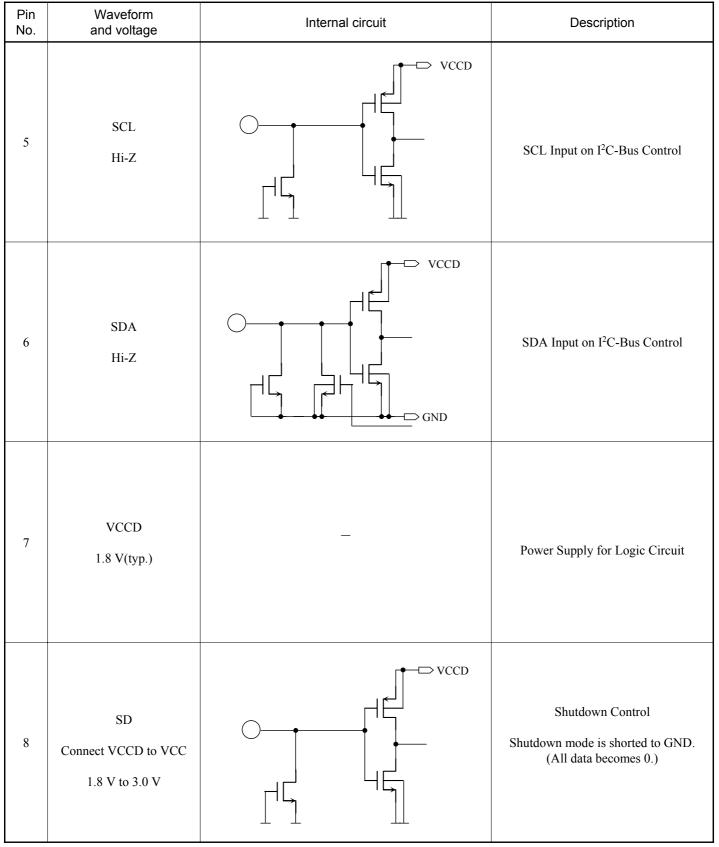

I/O block circuit diagrams and pin function descriptions Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No. | Waveform and voltage | Internal circuit | Description                              |

|------------|----------------------|------------------|------------------------------------------|

| 1          | VREF<br>DC 1.45 V    | VCC $\sim$       | Reference Voltage Output                 |

| 2          | PREOUT<br>DC 1.45 V  | S00 VCC          | Pre-amplifier Output                     |

| 3          | FB<br>DC 1.45 V      |                  | Pre-amplifier Negative<br>Feedback Input |

| 4          | GND                  |                  | Ground                                   |

• I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

• I/O block circuit diagrams and pin function descriptions (continued) Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No. | Waveform and voltage  | Internal circuit | Description                                       |

|------------|-----------------------|------------------|---------------------------------------------------|

| 9          | VCC<br>3.0 V(typ.)    |                  | Power Supply                                      |

| 10         | VREFSP<br>3.0 V(typ.) |                  | Reference Voltage Output<br>for Speaker Amplifier |

| 11         | OUT_NEG<br>DC 1.45 V  | -C               | Speaker Output<br>(Negative Phase)                |

| 12         | GNDSP                 |                  | Ground for<br>Speaker Amplifier                   |

• I/O block circuit diagrams and pin function descriptions (continued) Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No. | Waveform<br>and voltage | Internal circuit                                   | Description                           |

|------------|-------------------------|----------------------------------------------------|---------------------------------------|

| 13         | OUT_POS<br>DC 1.45 V    | VCCSP<br>VCCSP<br>VCCSP<br>VCCSP<br>VCCSP<br>GNDSP | Speaker Output<br>(Positive Phase)    |

| 14         | VCCSP<br>3.0 V(typ.)    |                                                    | Power Supply for<br>Speaker Amplifier |

| 15         | GND                     |                                                    | Ground                                |

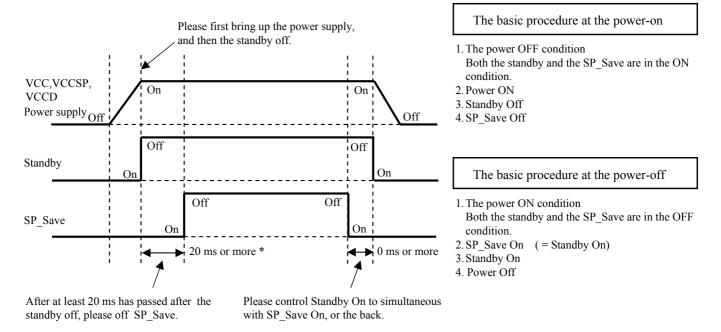

• Power supply and logic sequence

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

The timing control of power-ON/OFF and each logic according to the procedure below should be recommended for the best pop performance caused in switching.

1. The sequence of the power supply and each logic

Note) \*: This IC contains the pre-charge circuit. It is time until each bias is stabilized from Standby Off. It depends for this time on the capacity value linked to a reference voltage terminal (VREF and VREFSP), and the capacity value and resistance linked to an input terminal (IN).

It is a recommendation value in a constant given in the example of Application Circuit Example (Block Diagram).

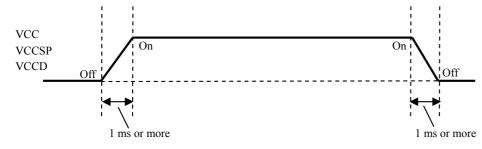

#### 2. The sequence of VCC and VCCSP and VCCD

This IC have not a standup and falling order in VCC and VCCSP. A standup and falling time of VCC and VCCSP recommend 1 or more ms.

- Technical Data (continued)

- $P_D T_a$  diagram

#### Usage Notes

- 1. Please take notice in the use of this product that it might break or occasionally smoke when an abnormal state occurs such as SP output pin (Pin11, Pin13) power supply pin short, SP output pin (Pin11, Pin13) GND short, or SP output (Pin11, Pin13) -to-SP output-pin short (load short).

- 2. Please absolutely do not mount the IC in the reverse direction on to the printed-circuit-board. It damaged when the electricity is turned on.

- 3. Please do not make it open, because the open SD-pin (Pin8) is not fixed.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805